## DOWNLOAD SOLVED FINAL

PAST PAPERS BY WAQAR SIDDHU

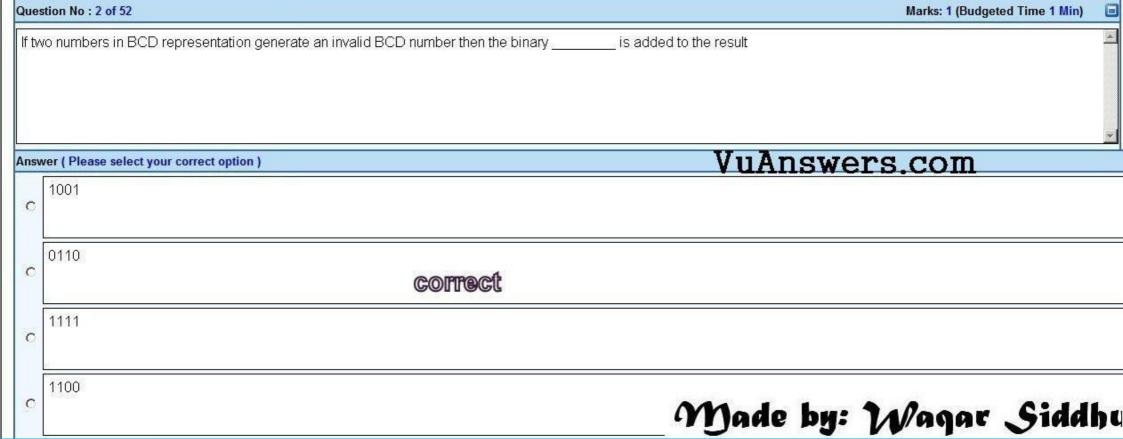

**More in PDF From**

VU Answer

**Get All Solutions.**

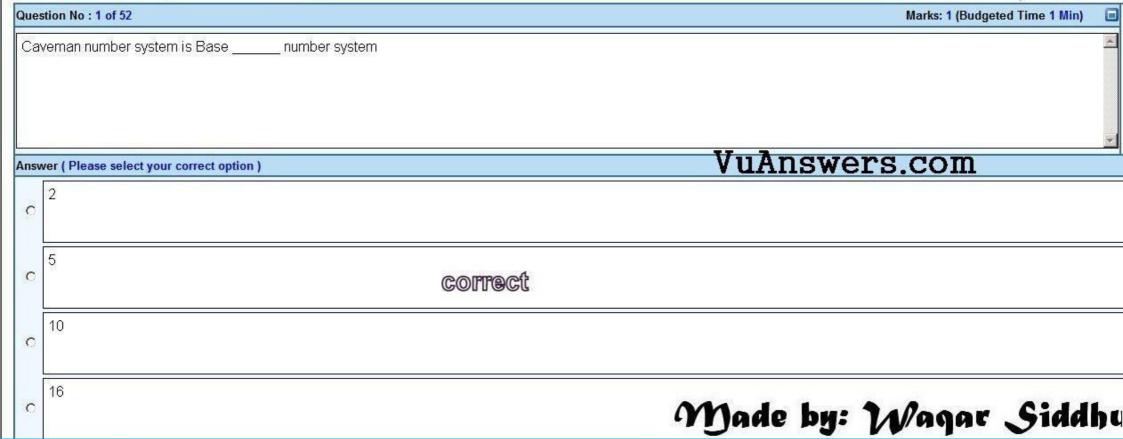

| Question No : 1 of 52                        |         | Marks: 1 (Budgeted Time 1 Min) |

|----------------------------------------------|---------|--------------------------------|

| The diagram given below represents           |         |                                |

| Answer ( Please select your correct option ) |         | VuAnswers.com                  |

| Demorgans law                                |         |                                |

| Associative law                              |         |                                |

| Product of sum form                          |         |                                |

| Sum of product form                          | correct | Made by: Wagar Siddhu          |

| Question No : 4 of 52                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Marks: 1 (Budgeted Time 1 Min) |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------|

| The simplest of the Encoders are the Encoders                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                |

| Answer ( Please select your correct option )                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | VuAnswers.com                  |

| C 2n-1-to-n                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                |

| n-to-2n                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                |

| 2n-to-n                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                |

| n-to-2n-1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                |

| ic The second se | Made by: Wagar Siddhu          |

| Question No : 5 of 52                                      |                              | Marks: 1 (Budgeted Time 1 Min) |     |

|------------------------------------------------------------|------------------------------|--------------------------------|-----|

| Using multiplexer as parallel to serial converter requires | connected to the multiplexer |                                | E E |

| Answer ( Please select your correct option )               |                              | VuAnswers.com                  |     |

| A parallel to serial converter circuit                     | correct                      |                                |     |

| A counter circuit                                          |                              |                                |     |

| A BCD to Decimal decoder                                   |                              |                                |     |

| A 2-to-8 bit decoder                                       |                              | Made by: Wagar Sidd            | ho  |

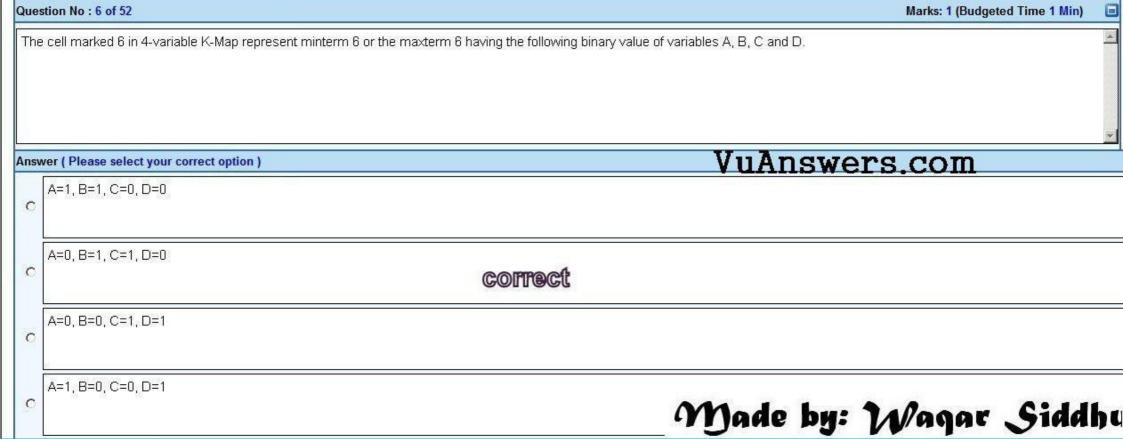

| Question No : 6 of 52                           | Marks: 1 (Budgeted Time 1 Min) |

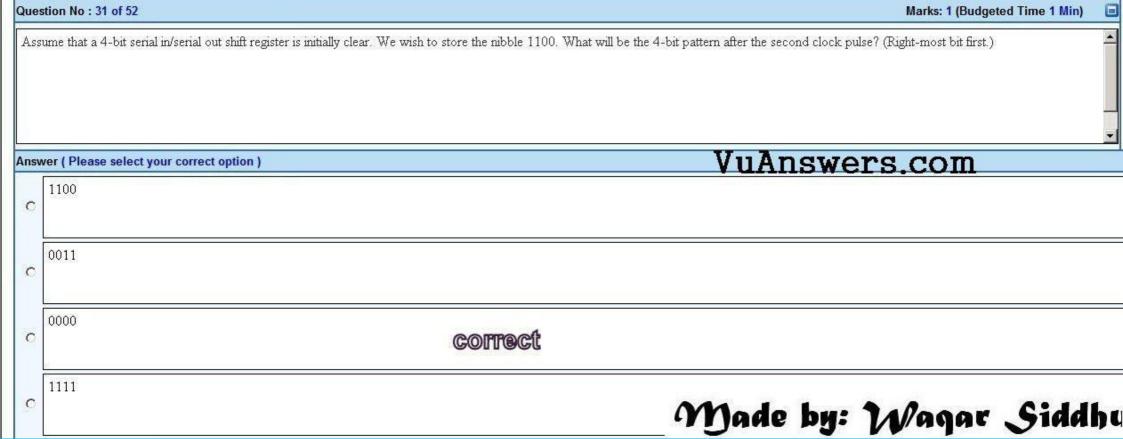

|-------------------------------------------------|--------------------------------|

| 74HC163 has two enable input pins which are and |                                |

| Answer ( Please select your correct option )    | VuAnswers.com                  |

| ENP, ENT                                        |                                |

| correct                                         |                                |

| ENI, ENC                                        |                                |

| ENP, ENC                                        |                                |

| ENT, ENI                                        | Made by: Wagar Siddhu          |

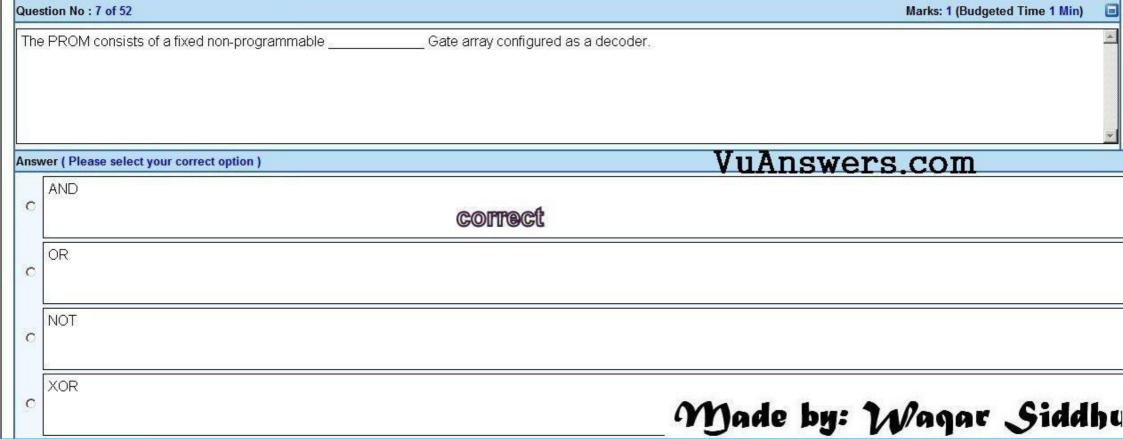

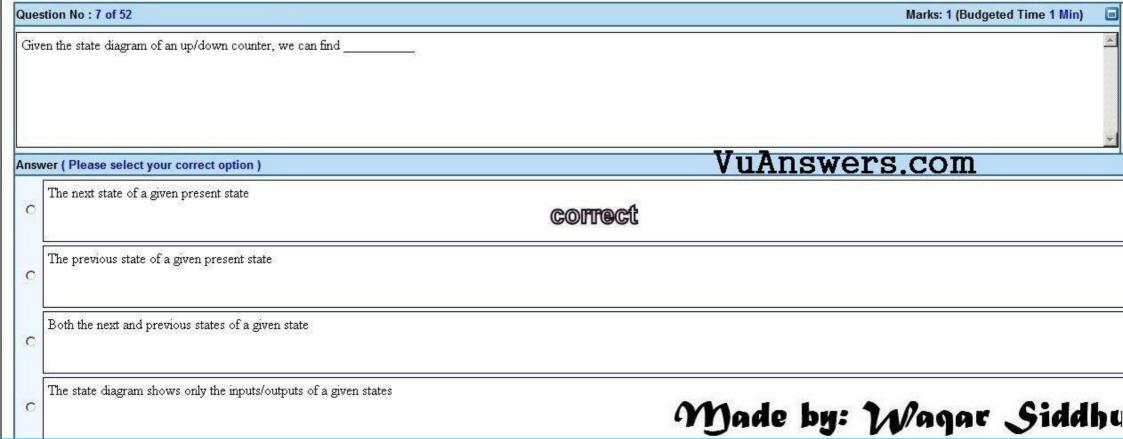

| Question No: 7 of 52                                              | Marks: 1 (Budgeted Time 1 Min) |

|-------------------------------------------------------------------|--------------------------------|

| Given the state diagram of an up/down counter, we can find        |                                |

| Answer ( Please select your correct option )                      | VuAnswers.com                  |

| The next state of a given present state                           |                                |

| The previous state of a given present state                       |                                |

| Both the next and previous states of a given state                | correct                        |

| The state diagram shows only the inputs/outputs of a given states | Made by: Wagar Siddhu          |

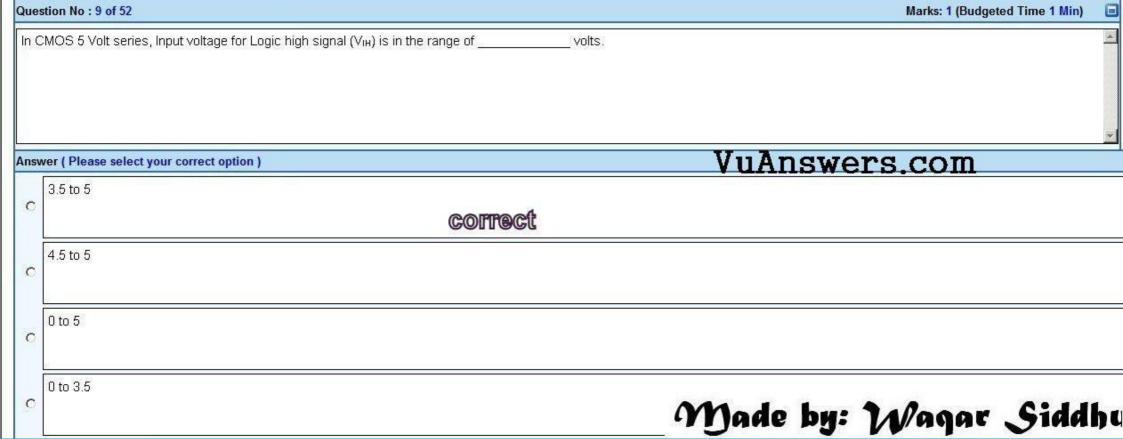

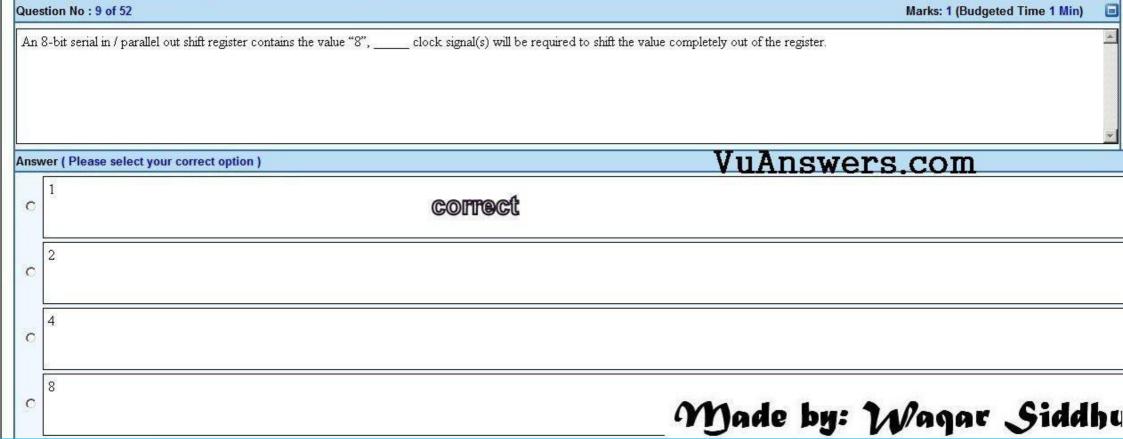

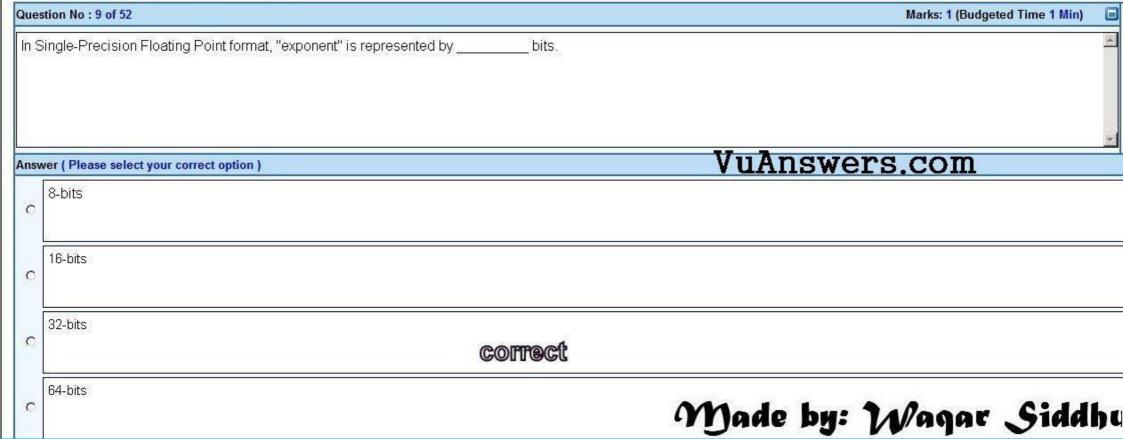

| Que  | estion No : 9 of 52                                      | Marks: 1 (Budgeted Time 1 Min) |

|------|----------------------------------------------------------|--------------------------------|

| (A   | $+B)(A+\overline{B}+C)(\overline{A}+C)$ is an example of |                                |

| Ansv | wer ( Please select your correct option )                | VuAnswers.com                  |

| c    | Product of sum form                                      |                                |

| c    | Sum of product form                                      |                                |

| 0    | Demorgans law                                            |                                |

| c    | Associative law                                          | Made by: Wagar Siddhu          |

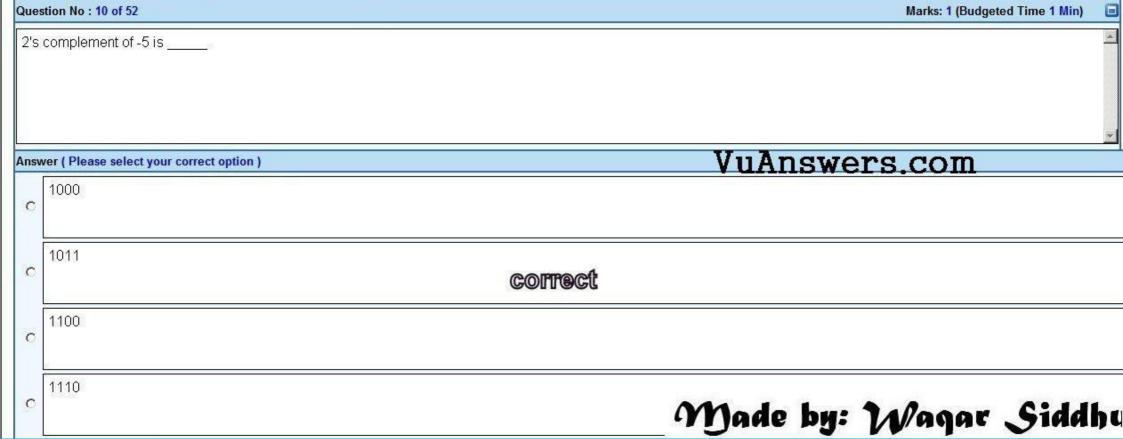

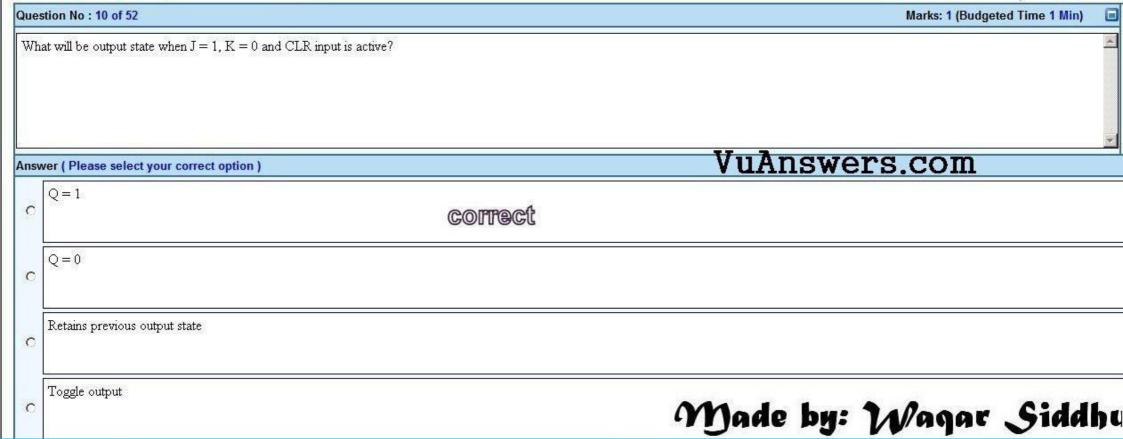

| Question No : 10 of 52                       | Marks: 1 (Budgeted Time 1 Min) |

|----------------------------------------------|--------------------------------|

| The 2's complement method is used to         |                                |

| Answer ( Please select your correct option ) | VuAnswers.com                  |

| Convert binary numbers to decimal            |                                |

| Convert decimal numbers to binary            |                                |

| Represent signed numbers                     | correct                        |

| Represent positive numbers                   | Made by: Wagar Siddhu          |

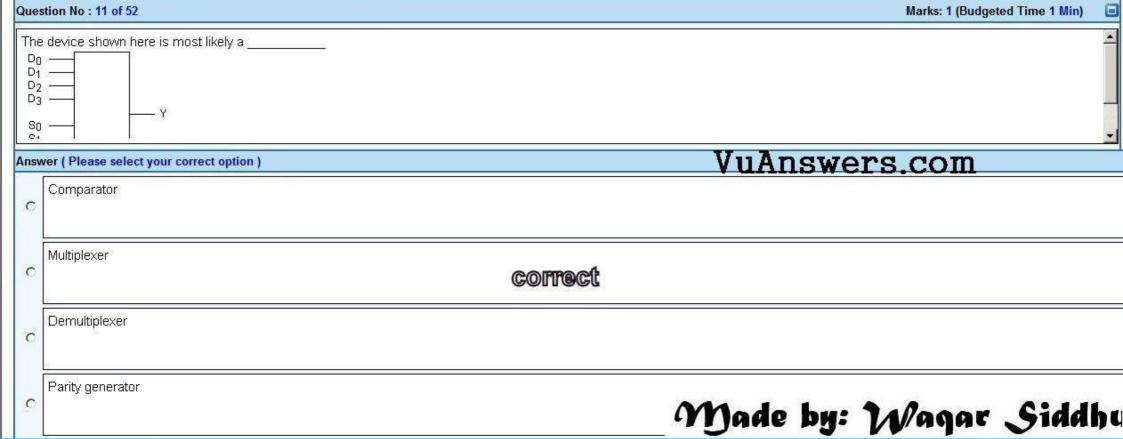

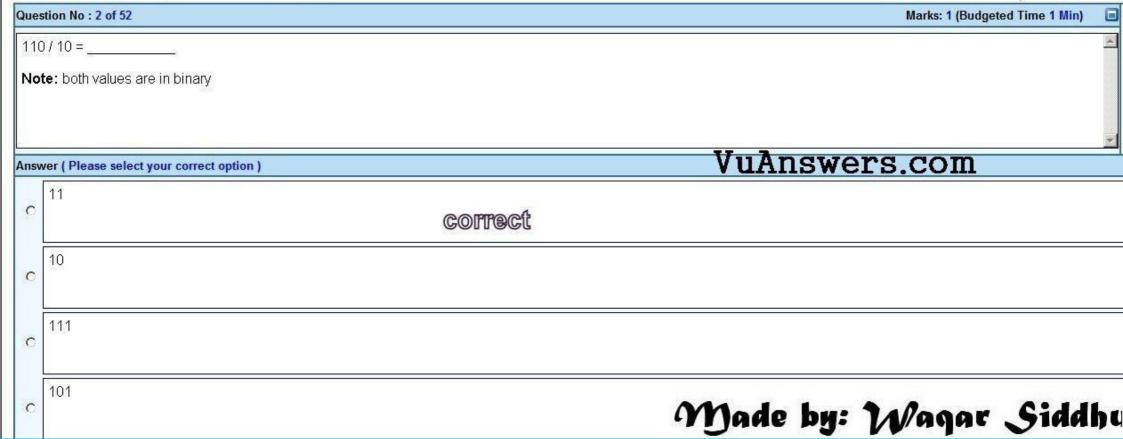

| Question No : 11 of 52                       | Marks: 1 (Budgeted Time 1 Min) |

|----------------------------------------------|--------------------------------|

| 1011 – 101 =                                 |                                |

| Note: both values are in binary              |                                |

|                                              |                                |

| Answer ( Please select your correct option ) | VuAnswers.com                  |

| 1100                                         |                                |

|                                              |                                |

| 0110                                         | mma a A                        |

| GO                                           | rrect                          |

| 0011                                         |                                |

|                                              |                                |

| 1001                                         |                                |

|                                              | Made by: Wagar Siddhu          |

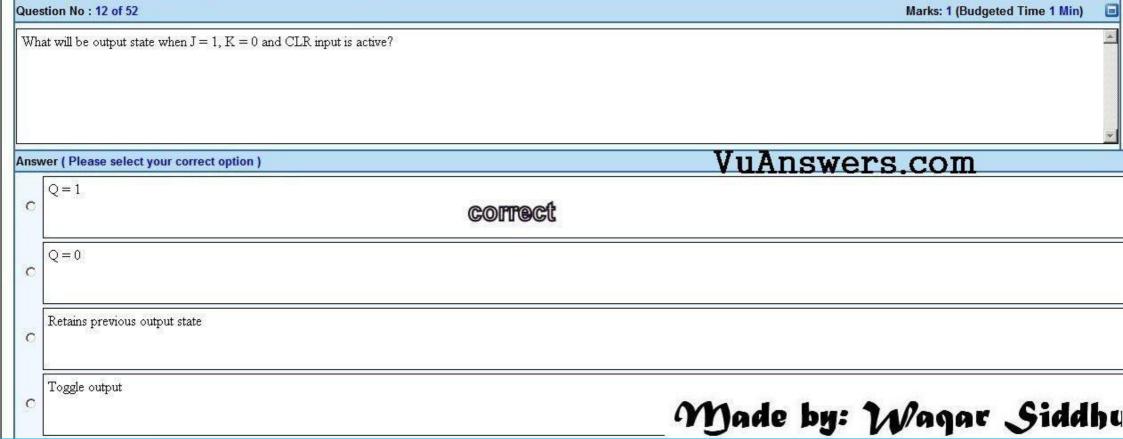

| Que | estion No : 12 of 52                             | Marks: 1 (Budgeted Time 1 Min) |

|-----|--------------------------------------------------|--------------------------------|

| At  | J = 1, and K = 1, output of JK Flip-flop will be |                                |

| Ans | wer ( Please select your correct option )        | VuAnswers.com                  |

| c   | Set                                              |                                |

| C   | Reset                                            |                                |

|     | Toggle                                           |                                |

| 0   | correct                                          |                                |

| c   | Invalid                                          | Made by: Wagar Siddhe          |

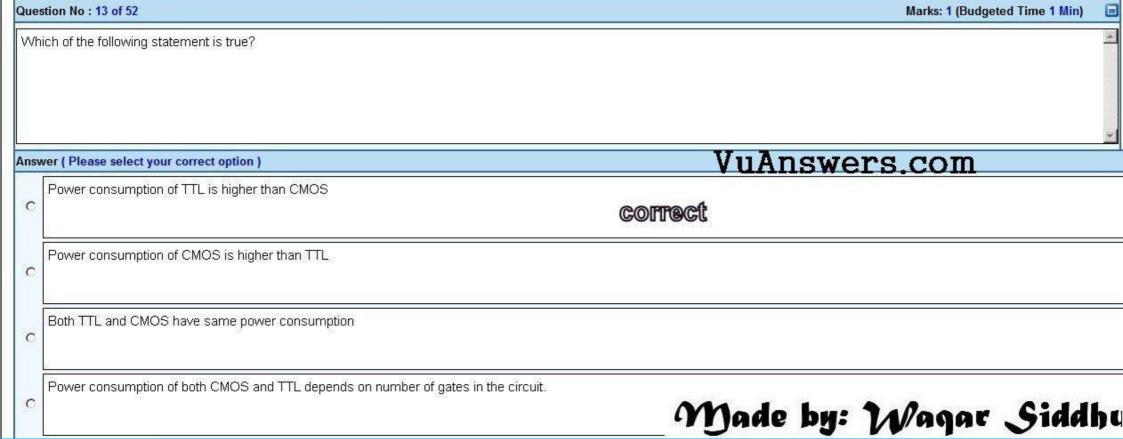

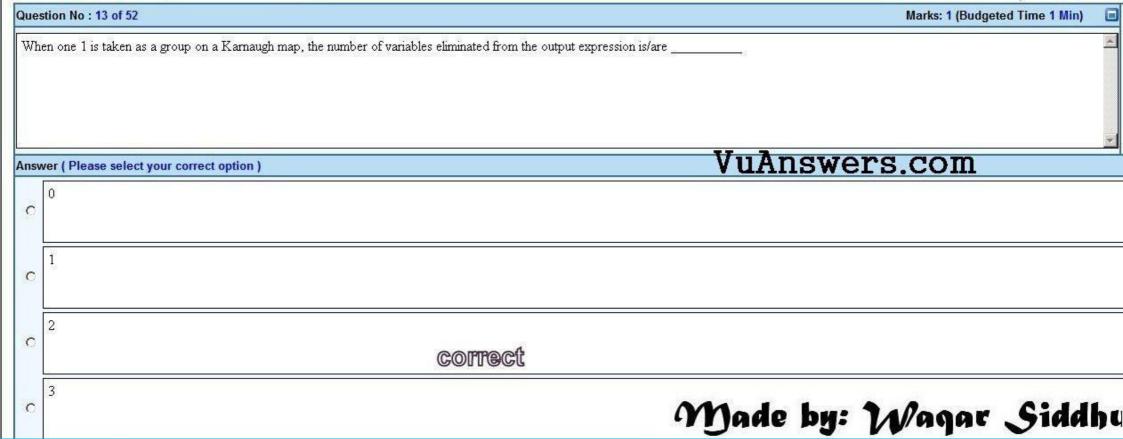

| ( | Question No: 13 of 52                                                                                                  | Marks: 1 (Budgeted Time 1 Min) |   |

|---|------------------------------------------------------------------------------------------------------------------------|--------------------------------|---|

|   | When one 1 is taken as a group on a Karnaugh map, the number of variables eliminated from the output expression is/are |                                | 4 |

| 1 | Answer ( Please select your correct option ) VUANSWE                                                                   | rs.com                         |   |

|   |                                                                                                                        |                                |   |

|   | i i                                                                                                                    |                                |   |

|   | 2                                                                                                                      |                                | _ |

|   | correct                                                                                                                |                                |   |

|   | <sup>3</sup> Made by:                                                                                                  | Wagar Siddh                    | L |

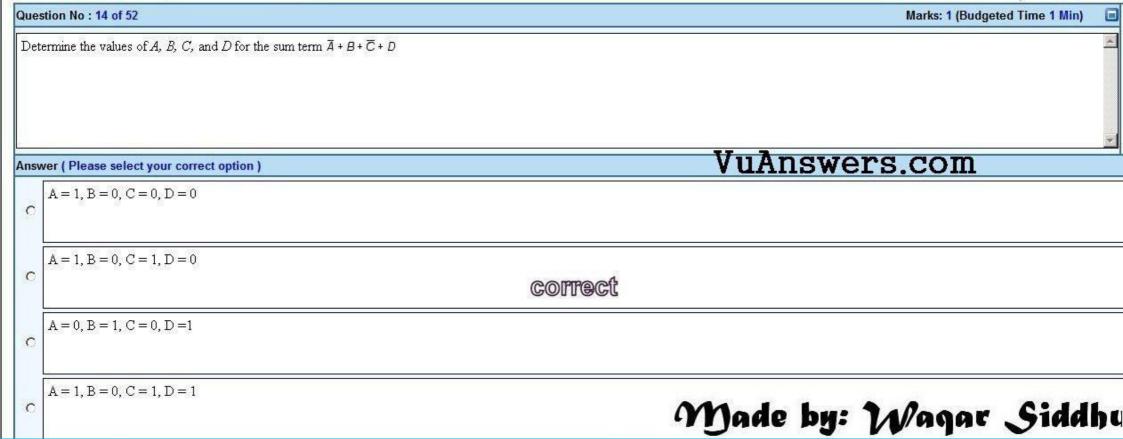

| Question No: 14 of 52                                                                             | Marks: 1 (Budgeted Time 1 Min) |

|---------------------------------------------------------------------------------------------------|--------------------------------|

| Using 15 digits (including the sign digit) notation the largest number that can be represented is |                                |

| Answer ( Please select your correct option )                                                      | VuAnswers.com                  |

| C 999,999,999 × 10100                                                                             |                                |

| 0.999,999,999 × 10100                                                                             |                                |

| 999,999,999 × 10 <sup>99</sup>                                                                    |                                |

| 0.999,999,999×10°° COFFECT                                                                        | Made by: Wagar Siddhu          |

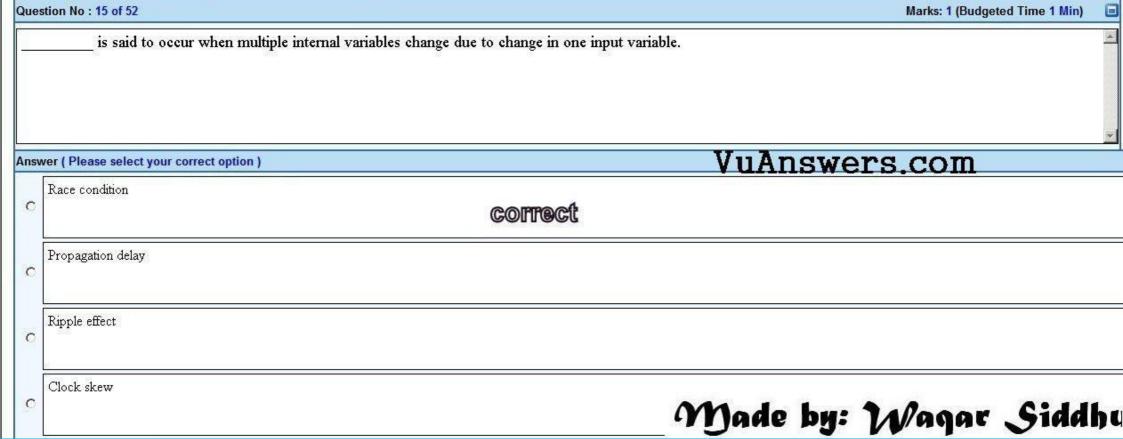

| Que | stion No : 15 of 52                               |                                                            | Marks: 1 (Budgeted Time 1 Min) |

|-----|---------------------------------------------------|------------------------------------------------------------|--------------------------------|

| The | e output of first 74HC163 counter is connected to | and inputs of other 74HC163 counter to form a single casca | ded counter                    |

| Ans | wer ( Please select your correct option )         | VuAns                                                      | swers.com                      |

| c   | RCO, ENT, ENP                                     | correct                                                    |                                |

| c   | ENT, RCO, ENP                                     |                                                            |                                |

| С   | ENP, RCO, ENT                                     |                                                            |                                |

| С   | RCO, ENI, ENC                                     | Made 1                                                     | by: Waqar Siddhu               |

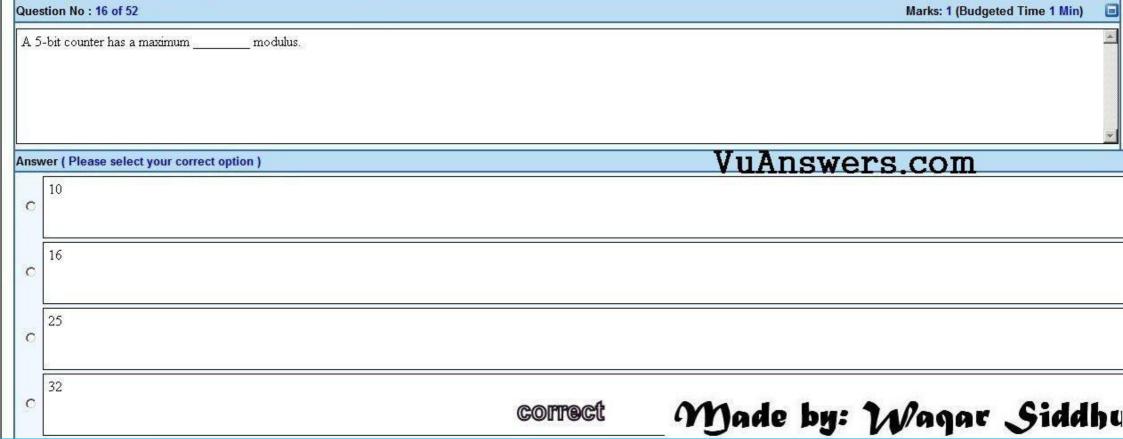

| Question No : 16 of 52                                                                     | Marks: 1 (Budgeted Time 1 Min) |

|--------------------------------------------------------------------------------------------|--------------------------------|

| The Sequential circuit whose output depends on the current state and the input is known as |                                |

| Answer ( Please select your correct option ) VuAn                                          | swers.com                      |

| Moore Machine                                                                              |                                |

| Mealy Machine  COFFECT                                                                     |                                |

| Counter                                                                                    |                                |

| Flip Flop  Made                                                                            | by: Waqar Siddhu               |

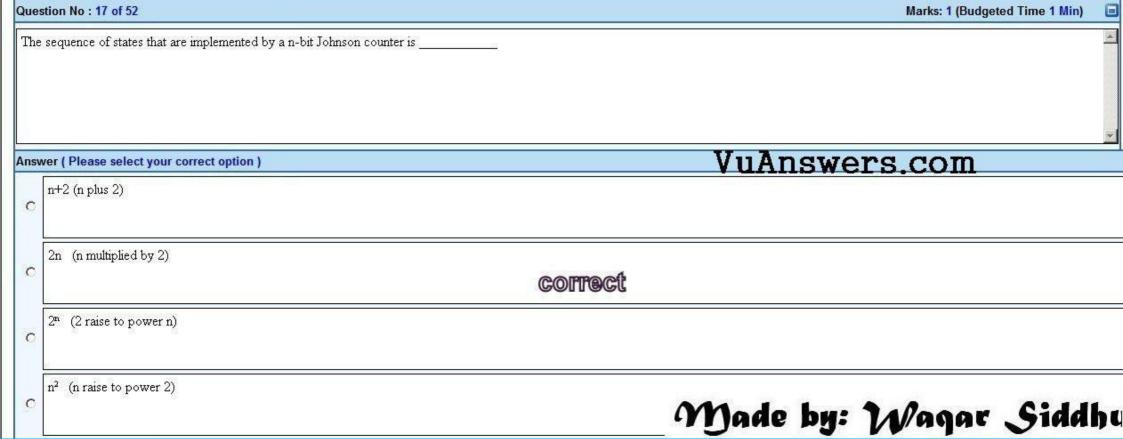

| Question No: 17 of 52                                                                  | Marks: 1 (Budgeted Time 1 Min) |

|----------------------------------------------------------------------------------------|--------------------------------|

| The best state assignment tends to                                                     |                                |

| Answer ( Please select your correct option )                                           | VuAnswers.com                  |

| Maximizes the number of state variables that don't change in a group of related states | correct                        |

| Minimizes the number of state variables that don't change in a group of related states |                                |

| Minimizes the equivalent states                                                        |                                |

| Maximizes the equivalent states                                                        | Made by: Waqar Siddhu          |

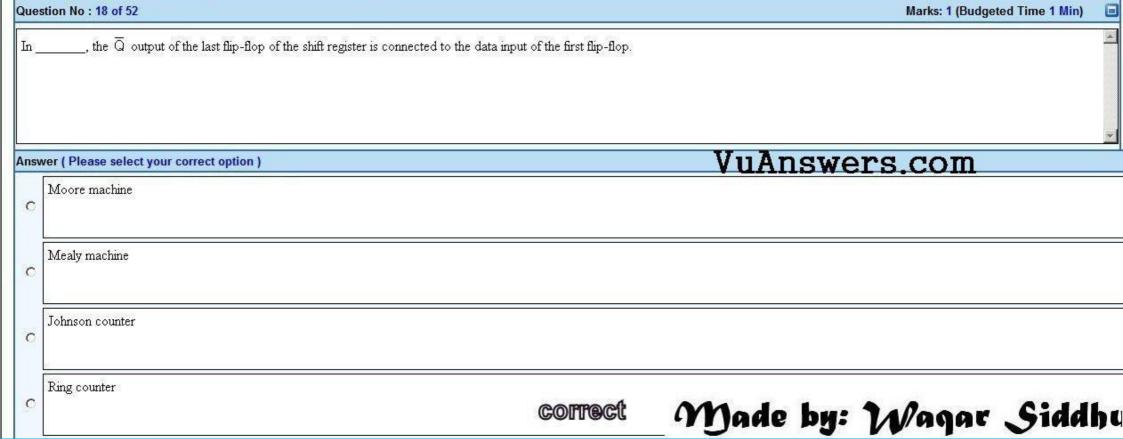

| Question No : 18 of 52                                                                                                        | Marks: 1 (Budgeted Time 1 Min) |

|-------------------------------------------------------------------------------------------------------------------------------|--------------------------------|

| In, the $\overline{\mathbb{Q}}$ output of the last flip-flop of the shift register is connected to the data input of the firs | it flip-flop.                  |

| Answer ( Please select your correct option )                                                                                  | VuAnswers.com                  |

| Moore machine                                                                                                                 |                                |

| Mealy machine                                                                                                                 |                                |

| Johnson counter  COFFEC                                                                                                       |                                |

| Ring counter                                                                                                                  | Made by: Waqar Siddhu          |

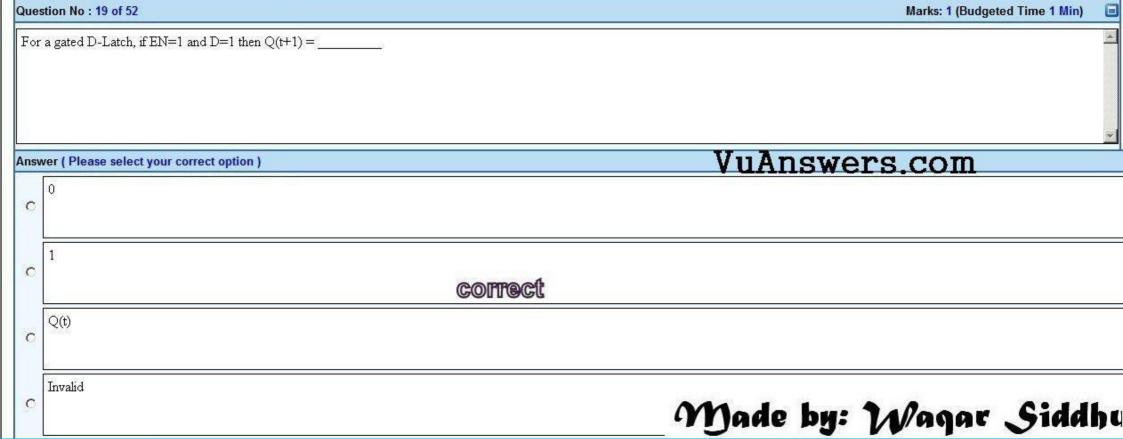

| Question No : 19 of 52                        |                                                           | Marks: 1 (Budgeted Time 1 Min)     |

|-----------------------------------------------|-----------------------------------------------------------|------------------------------------|

| In, the Q output of the last flip-flop of the | shift register is connected to the data input of the firs | t flip-flop of the shift register. |

| Answer ( Please select your correct option )  |                                                           | VuAnswers.com                      |

| Moore machine                                 |                                                           |                                    |

| Mealy machine                                 |                                                           |                                    |

| Johnson counter                               |                                                           |                                    |

| Ring counter                                  | correct                                                   | Made by: Wagar Siddhu              |

| Question No: 20 of 52                        | Marks: 1 (Budgeted Time 1 Min) |

|----------------------------------------------|--------------------------------|

| Flip flops are also called                   |                                |

| Answer ( Please select your correct option ) | VuAnswers.com                  |

| Bi-stable dualvibrators                      |                                |

| Bi-stable transformer                        |                                |

| Bi-stable multivibrators                     |                                |

|                                              | correct                        |

| C Bi-stable singlevibrators                  | Made by: Wagar Siddhu          |

| Question No : 21 of 52                                              | Marks: 1 (Budgeted Time 1 Min) |

|---------------------------------------------------------------------|--------------------------------|

| If S=1 and R=0, then Q(t+1) = for positive edge triggered flip-flop |                                |

| Answer ( Please select your correct option )                        | VuAnswers.com                  |

| correct                                                             |                                |

|                                                                     |                                |

| Invalid                                                             |                                |

| Input is invalid                                                    | Made by: Wagar Siddhu          |

| Question No : 22 of 52                                                                              | Marks: 1 (Budgeted Time 1 Min) |

|-----------------------------------------------------------------------------------------------------|--------------------------------|

| The operation of J-K flip-flop is similar to that of the SR flip-flop except that the J-K flip-flop |                                |

| Answer ( Please select your correct option )                                                        | VuAnswers.com                  |

| C Doesn't have an invalid state                                                                     |                                |

| Sets to clear when both J = 0 and K = 0                                                             |                                |

| It does not show transition on change in pulse                                                      |                                |

| It does not accept asynchronous inputs                                                              | Made by: Waqar Siddhu          |

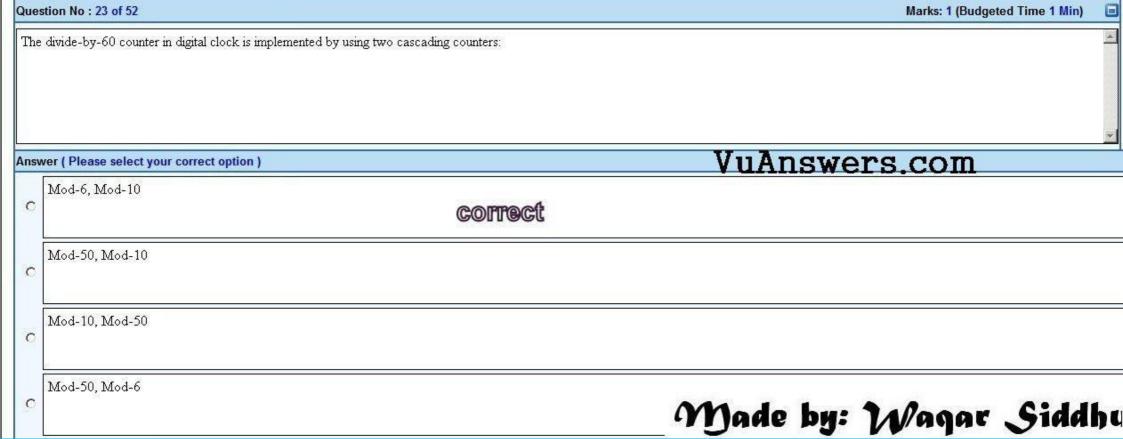

| Question No : 23 of 52                       | Marks: 1 (Budgeted Time 1 Min) |

|----------------------------------------------|--------------------------------|

| Flip-flops are obsolete now.                 |                                |

| Answer ( Please select your correct option ) | VuAnswers.com                  |

| Edge-triggered                               |                                |

| Master-Slave                                 |                                |

| correct                                      |                                |

| C T-Flip-flop                                |                                |

| C D-Flip-flop                                | Made by: Wagar Siddhu          |

| Question No : 24 of 52                                                                                  | Marks: 1 (Budgeted Time 1 Min) |

|---------------------------------------------------------------------------------------------------------|--------------------------------|

| Bi-stable devices remain in either of their states unless the inputs force the device to switch its sta | te.                            |

| Answer ( Please select your correct option )                                                            | VuAnswers.com                  |

| C Ten                                                                                                   |                                |

| Eight                                                                                                   |                                |

| Three                                                                                                   |                                |

| Two Correct                                                                                             | Made by: Wagar Siddhu          |

| Question No: 25 of 52                                                                                 | Marks: 1 (Budgeted Time 1 Min) |

|-------------------------------------------------------------------------------------------------------|--------------------------------|

| The counter states can be determined by the formula: ("n" represents the total number of flip-flops). |                                |

| Answer ( Please select your correct option ) VuAnswer                                                 | rs.com                         |

| C n² (n raise to power 2)                                                                             |                                |

| C n²-1 (n raise to power 2 and then minus 1)                                                          |                                |

| 2 <sup>n</sup> (2 raise to power n)                                                                   |                                |

| correct                                                                                               |                                |

| 2 <sup>n</sup> -1 (2 raise to power n and then minus 1)                                               |                                |

| 'YY)aae by:                                                                                           | Waqar Siddhi                   |

| Question No : 26 of 52                       |         | Marks: 1 (Budgeted Time 1 Min) |

|----------------------------------------------|---------|--------------------------------|

| RCO Stands for                               |         |                                |

| Answer ( Please select your correct option ) |         | VuAnswers.com                  |

| Reconfiguration Counter Output               |         |                                |

| Reconfiguration Clock Output                 |         |                                |

| Ripple Counter Output                        |         |                                |

| Ripple Clock Output                          | correct | Made by: Wagar Siddhu          |

| Question No : 27 of 52                         |                                             | Marks: 1 (Budgeted Time 1 Min) |

|------------------------------------------------|---------------------------------------------|--------------------------------|

| The Sequential circuit, whose output is detern | nined by the current state only is known as |                                |

| Answer ( Please select your correct option )   |                                             | VuAnswers.com                  |

| Moore Machine                                  | correct                                     |                                |

| Mealy Machine                                  |                                             |                                |

| Counter                                        |                                             |                                |

| Flip Flop                                      |                                             | Made by: Wagar Siddhu          |

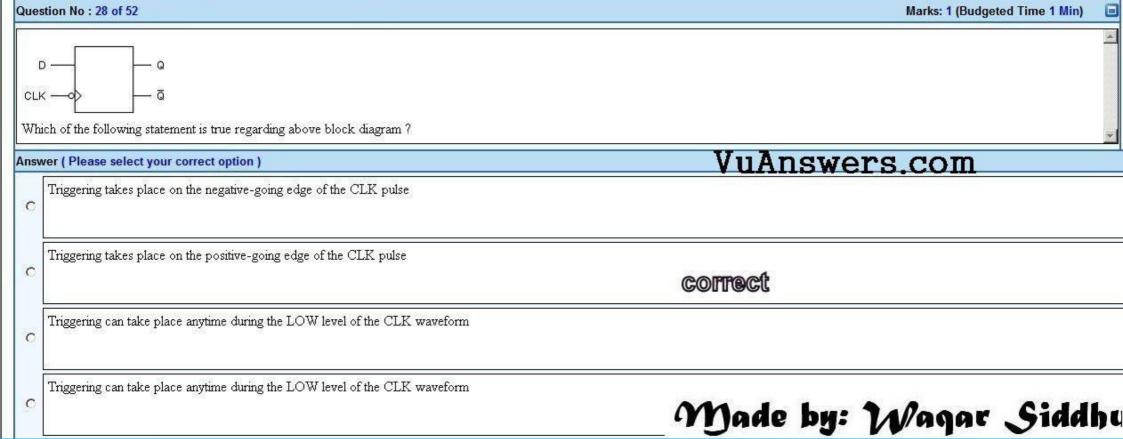

| Question No : 28 of 52                          |         | Marks: 1 (Budgeted Time 1 Min) |

|-------------------------------------------------|---------|--------------------------------|

| A GAL is essentially a                          |         |                                |

| Answer ( Please select your correct option )    |         | VuAnswers.com                  |

| Non-reprogrammable PAL                          |         |                                |

| PAL that is programmed only by the manufacturer |         |                                |

| Reprogrammable PAL                              | correct |                                |

| Reprogrammable PAL                              |         | Made by: Waqar Siddhu          |

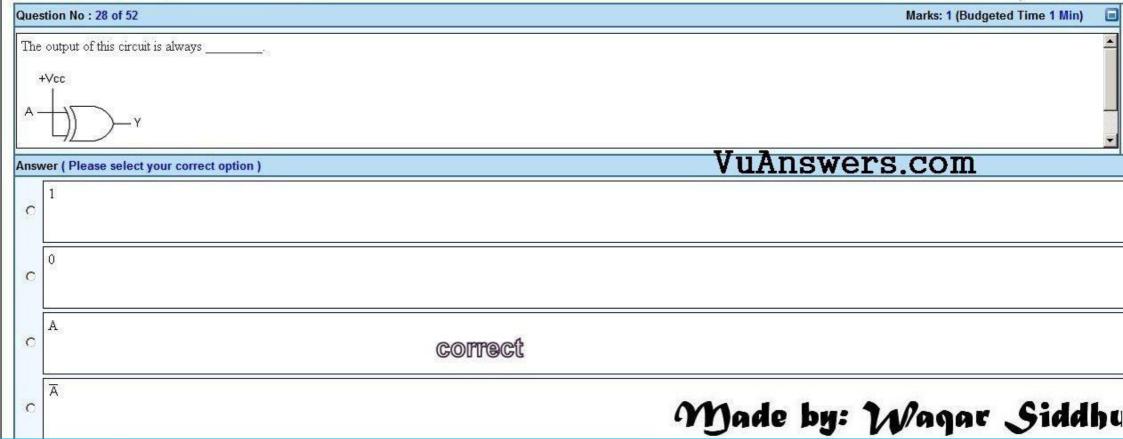

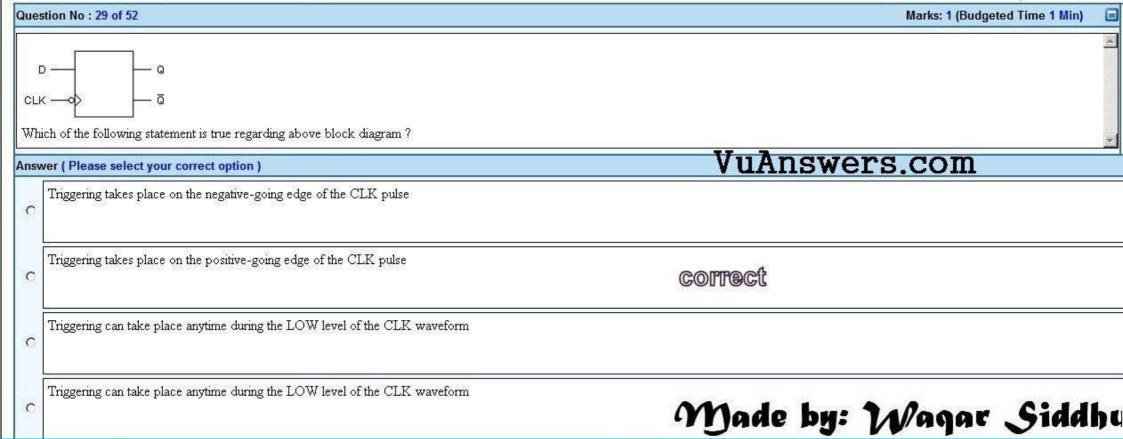

| Qı | uestion No : 29 of 52                       | Marks: 1 (Budgeted Time 1 Min) |    |

|----|---------------------------------------------|--------------------------------|----|

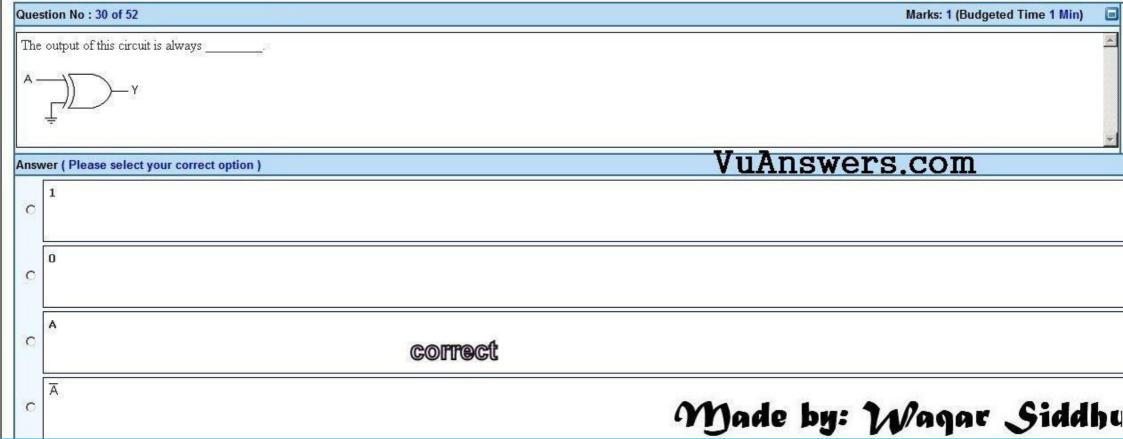

|    | he output of this circuit is always  +Vcc   |                                |    |

| Ar | nswer ( Please select your correct option ) | VuAnswers.com                  |    |

|    |                                             |                                |    |

|    | 0                                           |                                |    |

| 9  | Correct                                     |                                |    |

| 3  |                                             | Made by: Wagar Siddh           | C, |

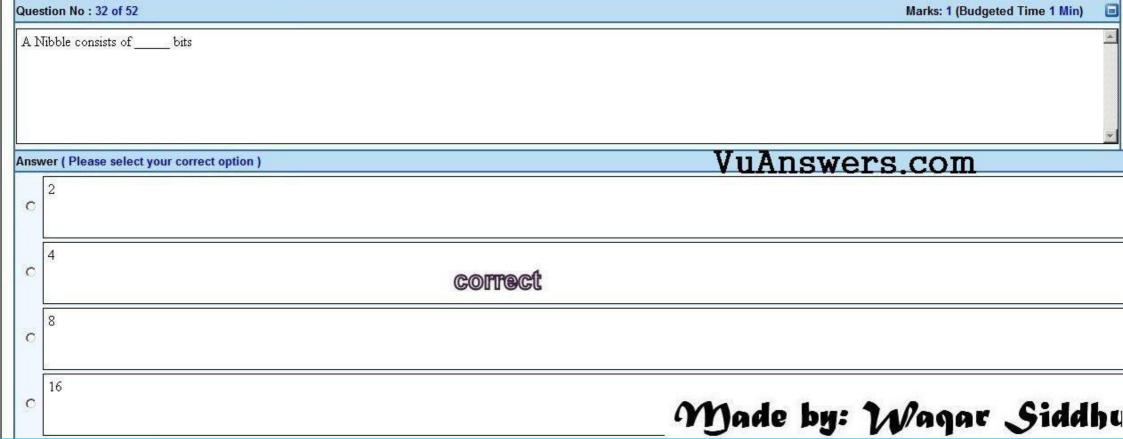

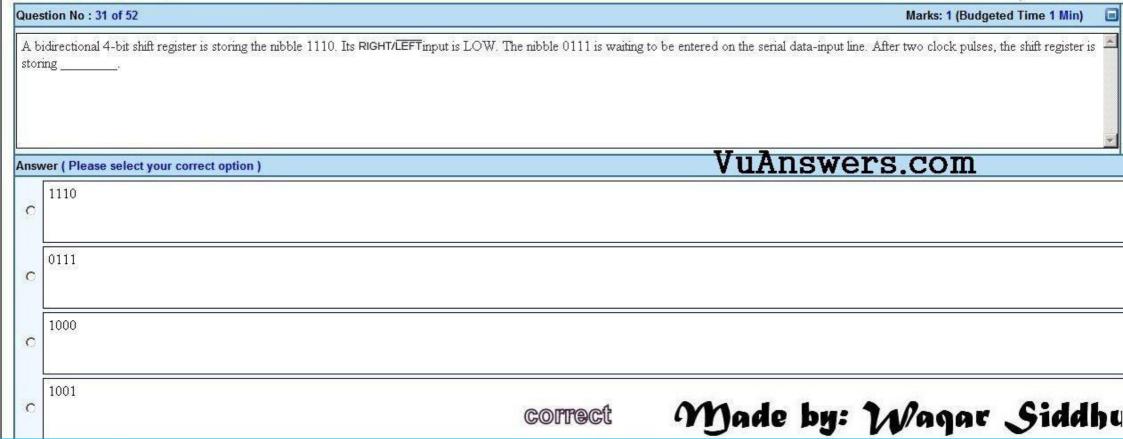

| Question No : 32 of 52                       |         | Marks: 1 (Budgeted Time 1 Min) |

|----------------------------------------------|---------|--------------------------------|

| Smallest unit of binary data is a            |         |                                |

| Answer ( Please select your correct option ) |         | VuAnswers.com                  |

| C Bit                                        | correct |                                |

| Nibble C                                     |         |                                |

| Byte                                         |         |                                |

| Word                                         |         | Made by: Wagar Siddhu          |

| Question No : 33 of 52                                                                                                                             | Marks: 1 (Budgeted Time 1 Min) |  |

|----------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------|--|

| The of a ROM is the time it takes for the data to appear at the Data Output of the ROM chip after an address is applied at the address input lines |                                |  |

| Answer ( Please select your correct option )                                                                                                       | VuAnswers.com                  |  |

| C Write Time                                                                                                                                       |                                |  |

| Refresh Time                                                                                                                                       |                                |  |

| Refresh Time                                                                                                                                       |                                |  |

| Access Time COFFECT                                                                                                                                | Made by: Waqar Siddhu          |  |

| Question No : 34 of 52                                          | Marks: 1 (Budgeted Time 1 Min) |

|-----------------------------------------------------------------|--------------------------------|

| In, all the columns in the same row are either read or written. |                                |

| Answer ( Please select your correct option )                    | VuAnswers.com                  |

| Sequential Access                                               |                                |

| MOS Access                                                      |                                |

| FAST Mode Page Access                                           |                                |

| COIT                                                            | rect                           |

| None of given options                                           | Made by: Waqar Siddhu          |

| Question No : 35 of 52                       |         | Marks: 1 (Budgeted Time 1 Min) |

|----------------------------------------------|---------|--------------------------------|

| FIFO is an acronym for                       |         |                                |

| Answer ( Please select your correct option ) |         | VuAnswers.com                  |

| First In, First Out                          | correct |                                |

| Fly in, Fly Out                              |         |                                |

| Fast in, Fast Out                            |         |                                |

| None of given options                        |         | Made by: Wagar Siddhu          |

| Question No : 36 of 52                                       | Marks: 1 (Budgeted Time 1 Min) |

|--------------------------------------------------------------|--------------------------------|

| If the FIFO Memory output is already filled with data then   |                                |

| Answer ( Please select your correct option )                 | VuAnswers.com                  |

| It is locked; no data is allowed to enter                    |                                |

| It is not locked; the new data overwrites the previous data. |                                |

| Previous data is swapped out of memory and new data enters   | correct                        |

| None of given options                                        | Made by: Wagar Siddhu          |

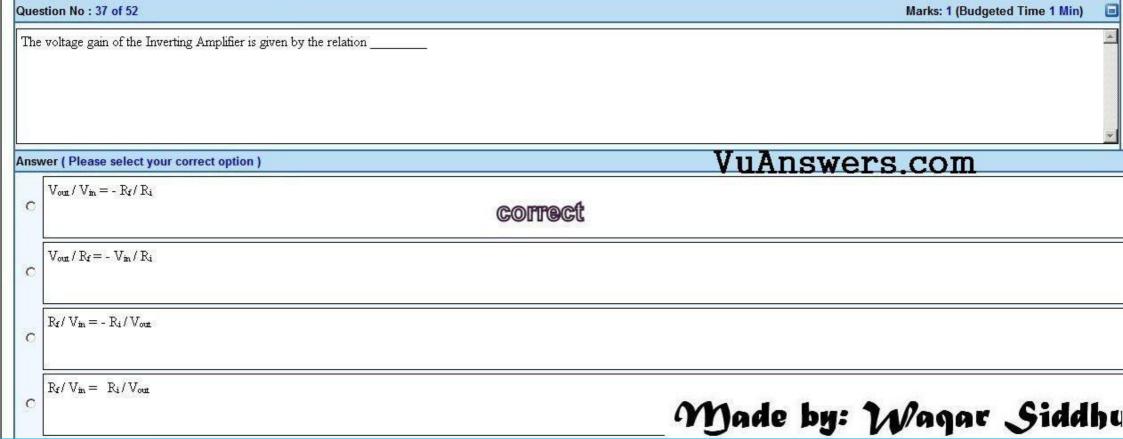

| Question No : 37 of 52                       | Marks: 1 (Budgeted Time 1 Min) | 0  |

|----------------------------------------------|--------------------------------|----|

| Stack is a                                   |                                |    |

| Answer ( Please select your correct option ) | VuAnswers.com                  |    |

| Bust Flash Memory                            |                                |    |

| FIFO memory                                  |                                |    |

| LIFO memory                                  |                                |    |

| C                                            | correct                        |    |

| Flash Memory                                 | Made by: Wagar Siddl           | hu |

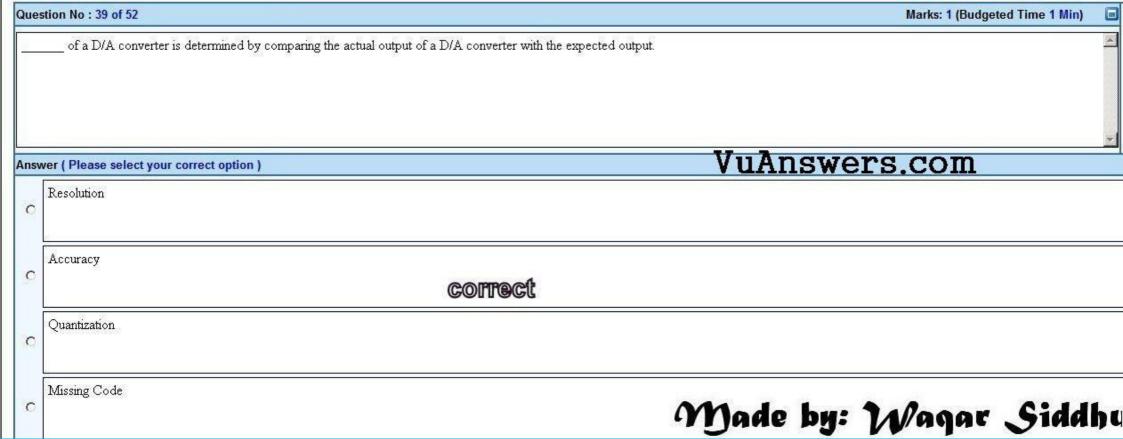

| Question No : 39 of 52 |                       | Marks: 1 (Budgeted Time 1 Min) |

|------------------------|-----------------------|--------------------------------|

| LUT is an acronym for  |                       |                                |

|                        |                       |                                |

|                        |                       | <u>*</u>                       |

| Answer ( Please select | your correct option ) | VuAnswers.com                  |

| Look Up Table          |                       |                                |

|                        | correct               |                                |

| Local User Termin      | nal                   |                                |

| Least Upper Time       | -T-3-4                |                                |

| C Least Opper Time     | : геноц               |                                |

| None of given opti     | tions                 |                                |

|                        |                       | Made by: Wagar Siddhu          |

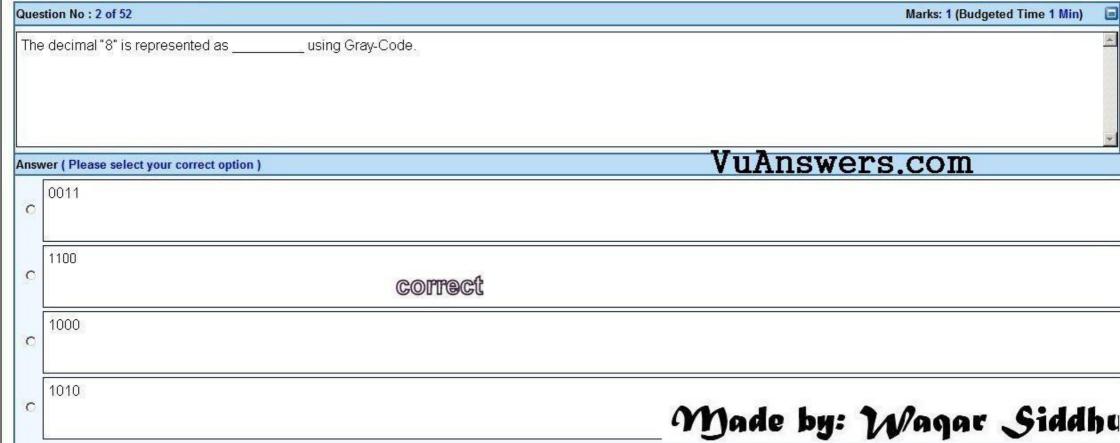

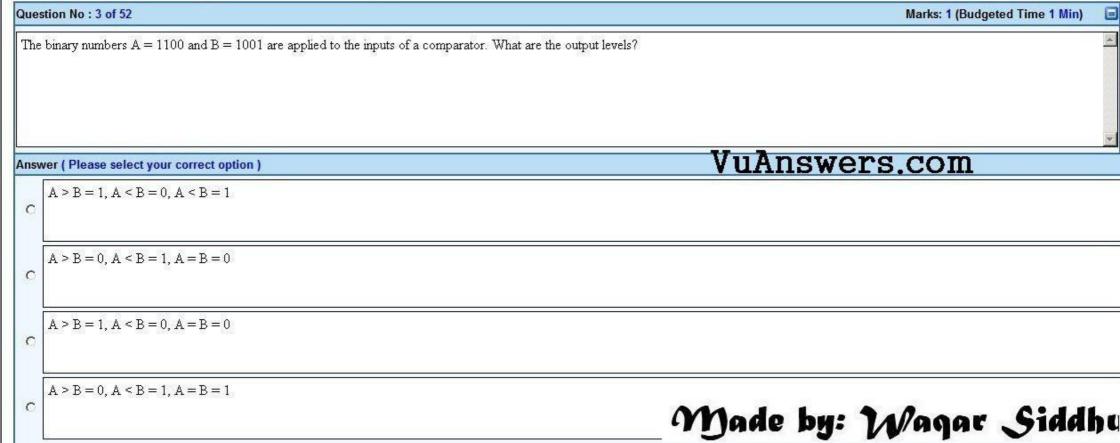

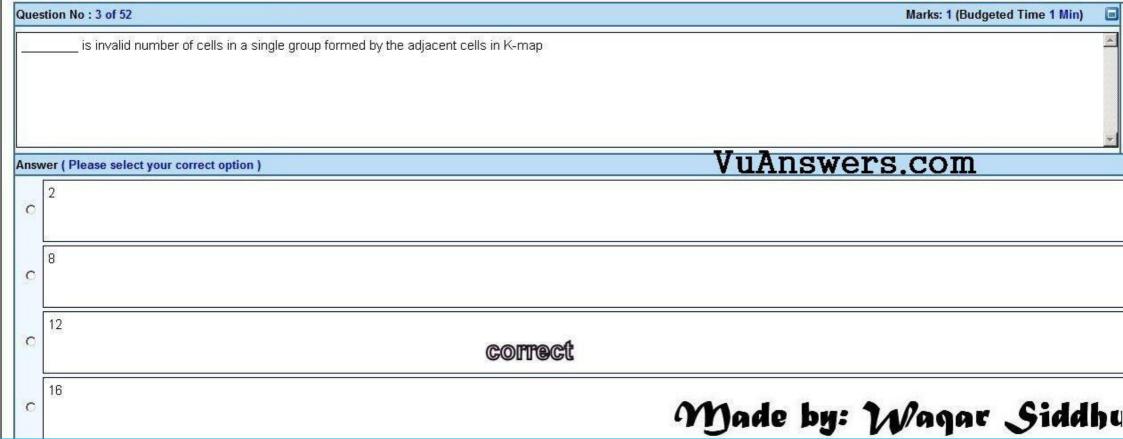

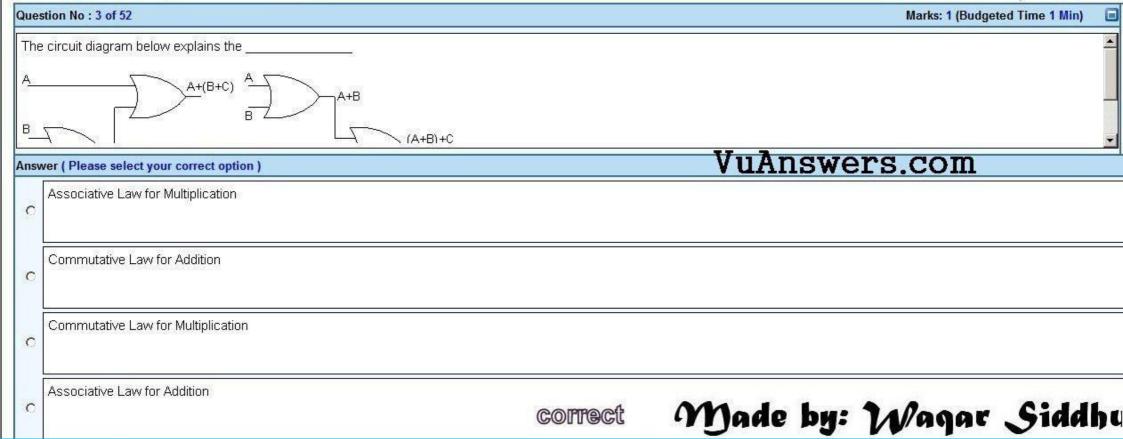

| Question No : 3 of 52                                            | Marks: 1 (Budgeted Time 1 Min) |

|------------------------------------------------------------------|--------------------------------|

| The Gray code is different from the unsigned binary code because |                                |

| Answer ( Please select your correct option )                     | VuAnswers.com                  |

| Successive values of Gray code differ by only one bit            | correct                        |

| Gray Code is positional code                                     |                                |

| Gray Code does not support negative values                       |                                |

| Gray Code ranges from "0" to "9"                                 | Made by: Wagar Siddhu          |

| Question No: 4 of 52                         | Marks: 1 (Budgeted Time 1 Min) |

|----------------------------------------------|--------------------------------|

| "74ALS" stands for                           |                                |

| Answer ( Please select your correct option ) | VuAnswers.com                  |

| Advanced Low-frequency Schottky TTL          | T GITTISWET S.COIII            |

| Advanced Low-dissipation Schottky TTL        |                                |

| Advanced Low-Power Schottky TTL              | a a manach                     |

|                                              | correct                        |

| Advanced Low-propagation Schottky TTL        | Made by: Wagar Siddhu          |

| Question No : 5 of 52                                              | Marks: 1 (Budgeted Time 1 Min) |

|--------------------------------------------------------------------|--------------------------------|

| The 3-variable Karnaugh Map (K-Map) has cells for min or max terms |                                |

| Answer ( Please select your correct option )                       | VuAnswers.com                  |

| c 4                                                                |                                |

| 8                                                                  |                                |

| correct                                                            | t e                            |

| c 12                                                               |                                |

| 16                                                                 |                                |

|                                                                    | Made by: Wagar Siddhe          |

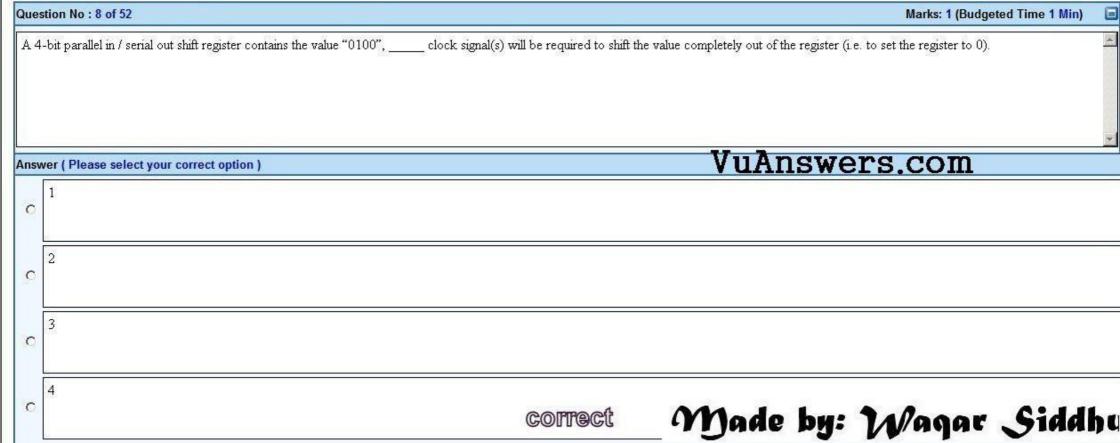

| Question No : 8 of 52                                       | Marks: 1 (Budgeted Time 1 Min) |

|-------------------------------------------------------------|--------------------------------|

| In a sequential circuit the next state is determined by and |                                |

| Answer ( Please select your correct option )                | VuAnswers.com                  |

| State variable, current state                               |                                |

| Current state, flip-flop output                             |                                |

| Current state and external input                            | correct                        |

| Input and clock signal applied                              |                                |

| C Input and clock signal applied                            | Made by: Wagar Siddhu          |

| Que  | estion No : 13 of 52                                                    | Marks: 1 (Budgeted Time 1 Min) |

|------|-------------------------------------------------------------------------|--------------------------------|

| The  | e binary values for the standard SOP expression, ABCD + ĀBCD + ĀBCD are |                                |

| Ansv | wer ( Please select your correct option )                               | VuAnswers.com                  |

| c    | 1110 + 0110 + 0001 <b>COFF</b>                                          |                                |

| С    | 1011 + 1111 + 1011                                                      |                                |

| С    | 0001 + 1001 + 1110                                                      |                                |

| С    | 1010 + 1110 + 0101                                                      | Made by: Wagar Siddho          |

| Question No : 14 of 52                                           |         | Marks: 1 (Budgeted Time 1 Min) |

|------------------------------------------------------------------|---------|--------------------------------|

| The design and implementation of synchronous counters start from |         |                                |

| Answer ( Please select your correct option )                     |         | VuAnswers.com                  |

| Truth table                                                      |         |                                |

| C K-map                                                          |         |                                |

| State table                                                      |         |                                |

| State diagram                                                    | correct | Made by: Wagar Siddhu          |

| Que  | estion No : 15 of 52                                                                        | Marks: 1 (Budgeted Time 1 Min) |

|------|---------------------------------------------------------------------------------------------|--------------------------------|

| In a | a state diagram, the transition from a current state to the next state is determined by and |                                |

| Ansv | wer ( Please select your correct option )                                                   | VuAnswers.com                  |

| c    | Current state, inputs                                                                       |                                |

| o    | Current state, outputs                                                                      |                                |

| c    | Previous state, inputs                                                                      |                                |

| c    | Previous state, outputs                                                                     | Made by: Wagar Siddho          |

| Question No : 18 of 52                       | Marks: 1 (Budgeted Time 1 Min) |

|----------------------------------------------|--------------------------------|

| Flip flops are also called                   |                                |

| Answer ( Please select your correct option ) | VuAnswers.com                  |

| Bi-stable dualvibrators                      |                                |

| Bi-stable transformer                        |                                |

| Bi-stable multivibrators                     | correct                        |

| Bi-stable singlevibrators                    | Made by: Wagar Siddhu          |

| Question No : 20 of 52                                                                         | Marks: 1 (Budgeted Time 1 Min) |

|------------------------------------------------------------------------------------------------|--------------------------------|

| The operation of J-K flip-flop is similar to that of the SR flip-flop except that the J-K flip | p-flop                         |

| Answer ( Please select your correct option )                                                   | VuAnswers.com                  |

| Doesn't have an invalid state                                                                  | correct                        |

| Sets to clear when both $J = 0$ and $K = 0$                                                    | 5 69 54 mag 25 41369           |

| It does not show transition on change in pulse                                                 |                                |

| It does not accept asynchronous inputs                                                         | Made by: Wagar Siddhu          |

| Question No : 21 of 52                                                                                                | Marks: 1 (Budgeted Time 1 Min) |

|-----------------------------------------------------------------------------------------------------------------------|--------------------------------|

| The minimum time for which the input signal has to be maintained at the input of flip-flop is called of the flip-flop | D                              |

| Answer ( Please select your correct option )                                                                          | VuAnswers.com                  |

| Set-up time                                                                                                           |                                |

| Pulse Stability time (PST)                                                                                            |                                |

| Hold time                                                                                                             |                                |

| correct                                                                                                               |                                |

| Pulse Interval time                                                                                                   | Made by: Wagar Siddhe          |

| Question No : | : 22 of 52                       | Marks: 1 (Budgeted Time 1 Min) |

|---------------|----------------------------------|--------------------------------|

| The           | input overrides the input        |                                |

| Answer ( Plea | ase select your correct option ) | VuAnswers.com                  |

| Asynchi       | ronous, synchronous              | correct                        |

| Synchro       | onous, asynchronous              |                                |

| Preset in     | input (PRE), clear input (CLR)   |                                |

| Clear in      | nput (CLR), preset input (PRE)   | Made by: Wagar Siddhu          |

| Question No : 24 of 52                       | Marks: 1 (Budgeted Time 1 Min) |

|----------------------------------------------|--------------------------------|

| The hours counter is implemented using       |                                |

|                                              | <b>▼</b>                       |

| Answer ( Please select your correct option ) | VuAnswers.com                  |

| Mod-10 and Mod-2 counters                    |                                |

| A single decade counter and a flip-flop      |                                |

| c                                            | correct                        |

| Only a single Mod-12 counter is required     |                                |

| Mod-10 and Mod-6 counters                    | Made by: Wagar Siddho          |

| Question No : 25 of 52                       | Marks: 1 (Budgeted Time 1 Min) |

|----------------------------------------------|--------------------------------|

| State Machine is a generic name given to     |                                |

| Answer ( Please select your correct option ) | VuAnswers.com                  |

| Sequential circuits                          |                                |

|                                              | correct                        |

| Combinational circuits                       |                                |

| Flip-flops                                   |                                |

| Counters                                     | Made by: Wagar Siddhu          |

| Question I | No : 26 of 52                                                   | Marks: 1 (Budgeted Time 1 Min) |

|------------|-----------------------------------------------------------------|--------------------------------|

|            | is used to simplify the circuit that determines the next state. |                                |

| Answer ( I | Please select your correct option )                             | VuAnswers.com                  |

| State      | e diagram                                                       |                                |

| Nex        | t state table                                                   |                                |

| State      | e reduction                                                     |                                |

| State      | e assignment COFFO                                              | Made by: Wagar Siddhu          |

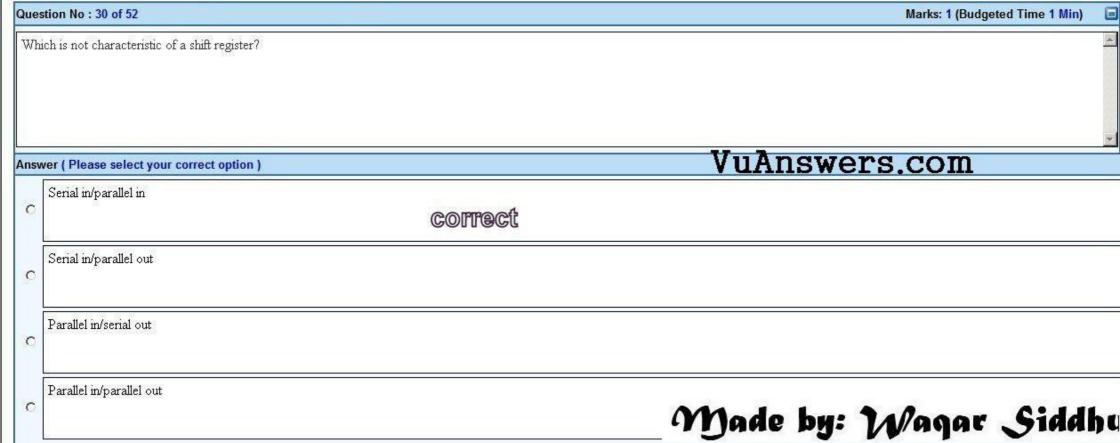

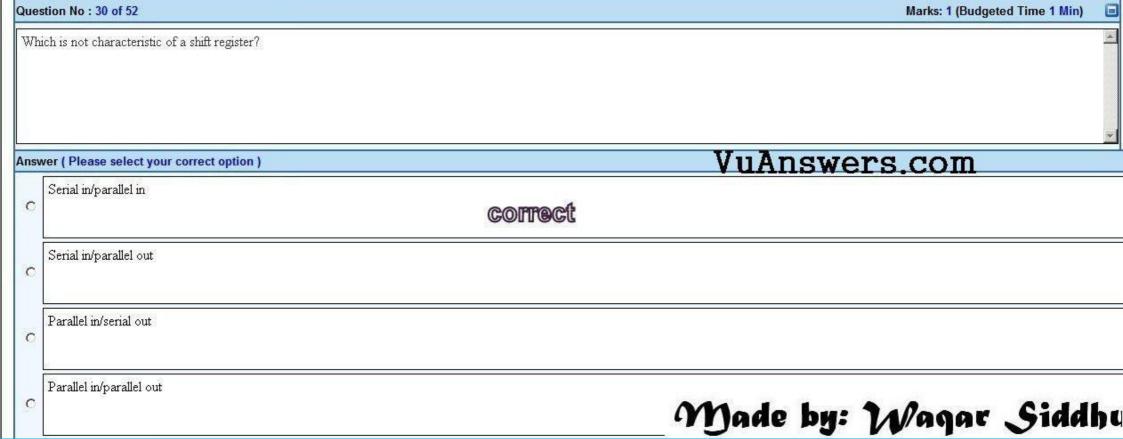

| Question No : 27 of 52                                                     | Marks: 1 (Budgeted Time 1 Min) |

|----------------------------------------------------------------------------|--------------------------------|

| The alternate solution for a demultiplexer-register combination circuit is |                                |

| Answer ( Please select your correct option )                               | VuAnswers.com                  |

| Parallel in / Serial out shift register                                    |                                |

| Serial in / Parallel out shift register                                    | correct                        |

| Parallel in / Parallel out shift register                                  |                                |

| Serial in / Serial Out shift register                                      | Made by: Wagar Siddho          |

| Question No : 28 of 52                                                                      | Marks: 1 (Budgeted Time 1 Min) |

|---------------------------------------------------------------------------------------------|--------------------------------|

| In the following statement Z PIN 20 ISTYPE 'reg.invert'; The keyword "reg.invert" indicates |                                |

| Answer ( Please select your correct option )                                                | VuAnswers.com                  |

| An inverted register input                                                                  |                                |

| An inverted register input at pin 20                                                        |                                |

| Active-high Registered Mode output                                                          |                                |

| Active-low Registered Mode output                                                           | correct Made by: Wagar Siddhu  |

| Question No : 29 of 52                          | Marks: 1 (Budgeted Time 1 Min | 1) 🖃 |

|-------------------------------------------------|-------------------------------|------|

| A GAL is essentially a                          |                               | A    |

| Answer ( Please select your correct option )    | VuAnswers.com                 | ₽    |

| Non-reprogrammable PAL                          |                               |      |

| PAL that is programmed only by the manufacturer |                               |      |

| Reprogrammable PAL                              | correct                       |      |

| Reprogrammable PAL                              | Made by: Wagar Side           | dha  |

| Question No : 33 of 52                                   |         | Marks: 1 (Budgeted Time 1 Min) |

|----------------------------------------------------------|---------|--------------------------------|

| The address, from which the data is read, is provided by |         |                                |

| Answer ( Please select your correct option )             |         | VuAnswers.com                  |

| Depends on circuitry                                     |         |                                |

| None of given options                                    |         |                                |

| CRAM                                                     |         |                                |

| Microprocessor                                           | correct | Made by: Wagar Siddho          |

| Question No : 34 of 52                       | Marks: 1 (Budgeted Time 1 Min) |

|----------------------------------------------|--------------------------------|

| FIFO is an acronym for                       |                                |

| Answer ( Please select your correct option ) | VuAnswers.com                  |

| First In, First Out                          | correct                        |

| Fly in, Fly Out                              |                                |

| Fast in, Fast Out                            |                                |

| None of given options                        | Made by: Wagar Siddho          |

| Question No : 35 of 52                                                                           | Marks: 1 (Budgeted Time 1 Min) |

|--------------------------------------------------------------------------------------------------|--------------------------------|

| In order to synchronize two devices that consume and produce data at different rates, we can use |                                |

| Answer ( Please select your correct option )                                                     | VuAnswers.com                  |

| Read Only Memory                                                                                 |                                |

| First In First Out Memory                                                                        | ect                            |

| Flash Memory                                                                                     |                                |

| Fast Page Access Mode Memory                                                                     | Made by: Wagar Siddhu          |

| Question No : 36 of 5 | 52                                           | Marks: 1 (Budgeted Time 1 Min) |

|-----------------------|----------------------------------------------|--------------------------------|

| If the FIFO Memory    | y output is already filled with data then    |                                |

| Answer ( Please sele  | ect your correct option )                    | VuAnswers.com                  |

| It is locked; no      | data is allowed to enter                     |                                |

| It is not locked;     | ; the new data overwrites the previous data. |                                |

| Previous data is      | s swapped out of memory and new data enters  |                                |

| None of given of      | options COFFE                                | t Made by: Waqar Siddhu        |

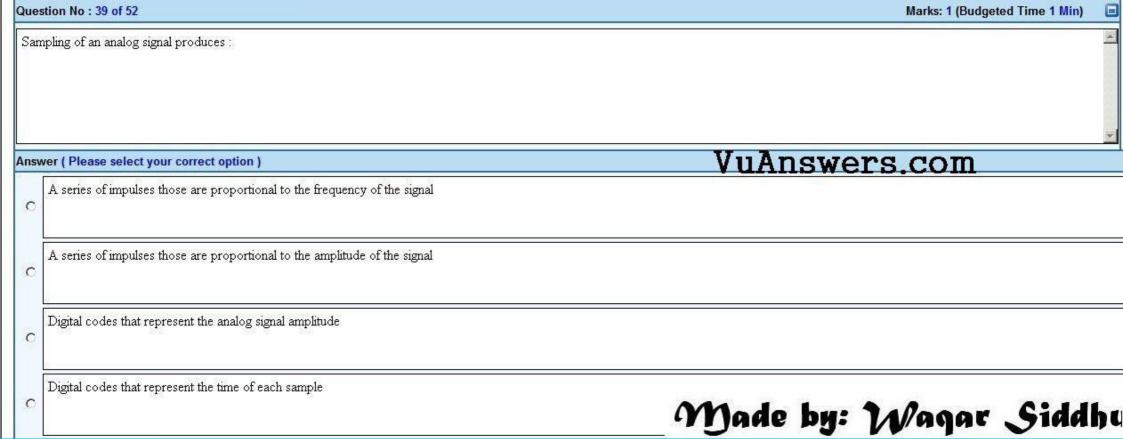

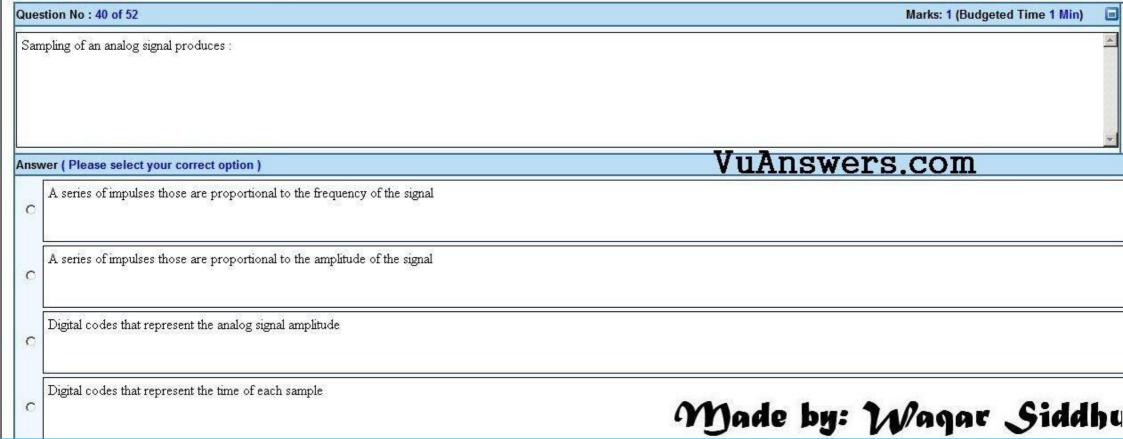

| Question No : 38 of 52                                                                         | Marks: 1 (Budgeted Time 1 Min) |

|------------------------------------------------------------------------------------------------|--------------------------------|

| The process of converting the analogue signal into a digital representation (code) is known as |                                |

| Answer ( Please select your correct option )                                                   | VuAnswers.com                  |

| Strobing                                                                                       |                                |

| Amplification                                                                                  |                                |

| Quantization                                                                                   |                                |

| COPT                                                                                           | ect                            |

| Digitization                                                                                   | Made by: Wagar Siddhu          |

| Question No : 3 of 52                                              | Marks: 1 (Budgeted Time 1 Min) |

|--------------------------------------------------------------------|--------------------------------|

| The 3-variable Karnaugh Map (K-Map) has cells for min or max terms |                                |

| Answer ( Please select your correct option )                       | VuAnswers.com                  |

| c 4                                                                |                                |

| 8                                                                  |                                |

| 12                                                                 |                                |

|                                                                    |                                |

| COFFECT                                                            | Made by: Wagar Siddhu          |

| Question No : 5 of 52                                                               | Marks: 1 (Budgeted Time 1 Min) |

|-------------------------------------------------------------------------------------|--------------------------------|

| Two 2-input, 4-bit multiplexers 74X157 can be connected to implement a multiplexer. |                                |

| Answer ( Please select your correct option )                                        | VuAnswers.com                  |

| 2-input, 4-bit                                                                      |                                |

| 4-input, 8-bit                                                                      |                                |

| 4-input, 16-bit                                                                     |                                |

| 2-input, 8-bit                                                                      | Made by: Wagar Siddho          |

| Question No : 6 of 52                        | Marks: 1 (Budgeted Time 1 Min) |

|----------------------------------------------|--------------------------------|

| GAL is an acronym for                        |                                |

| Answer ( Please select your correct option ) | VuAnswers.com                  |

| Generic Analysis Logic                       |                                |

| Giant Array Logic                            |                                |

| General Array Logic                          |                                |

| Generic Array Logic                          | correct Made by: Wagar Siddhe  |

| Ques | stion No : 7 of 52                            | Marks: 1 (Budgeted Time 1 Min) |

|------|-----------------------------------------------|--------------------------------|

| 74H  | IC163 has two enable input pins which are and |                                |

| Answ | ver ( Please select your correct option )     | VuAnswers.com                  |

| c    | ENP, ENT COFFECT                              |                                |

| c    | ENI, ENC                                      |                                |

| c    | ENP, ENC                                      |                                |

| C    | ENT, ENI                                      | Made by: Wagar Siddhu          |

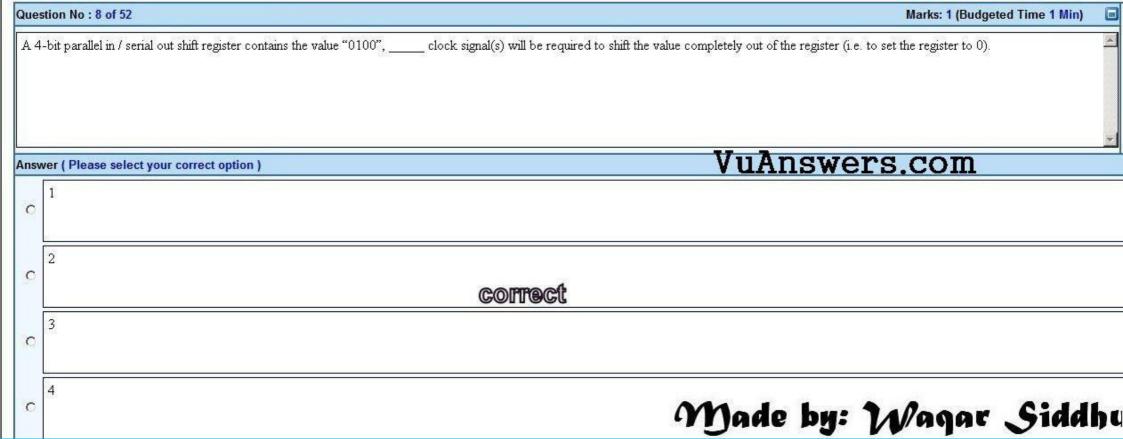

| Question | n No : 8 of 52                        | Marks: 1 (Budgeted Time 1 Min) |

|----------|---------------------------------------|--------------------------------|

| A.(B+    | C) = A.B + A.C is an expression of    |                                |

| Answer   | ( Please select your correct option ) | VuAnswers.com                  |

| C De     | emorgan's Law                         | V UIIIDWCLD.COM                |

| C        | ommutative Law                        |                                |

| C Di     | istributive Law                       |                                |

| C As     | ssociative Law                        | Made by: Wagar Siddho          |

| Que | estion No : 14 of 52                                             | Marks: 1 (Budgeted Time 1 Min) |

|-----|------------------------------------------------------------------|--------------------------------|

|     | counters as the name indicates are not triggered simultaneously. |                                |

| Ans | wer ( Please select your correct option )                        | VuAnswers.com                  |

| c   | Synchronous                                                      |                                |

| c   | Asynchronous                                                     | ect                            |

| c   | Positive-Edge triggered                                          |                                |

| C   | Negative-Edge triggered                                          | Made by: Wagar Siddhu          |

| Question No : 17 of 52                                                                     | Marks: 1 (Budgeted Time 1 Min) |

|--------------------------------------------------------------------------------------------|--------------------------------|

| The Sequential circuit whose output depends on the current state and the input is known as |                                |

| Answer ( Please select your correct option )                                               | VuAnswers.com                  |

| Moore Machine                                                                              |                                |

| Mealy Machine                                                                              |                                |

| correct                                                                                    |                                |

| Counter                                                                                    |                                |

| Flip Flop                                                                                  | Made by: Wagar Siddho          |

| Que  | estion No: 20 of 52                                                                                                    | Marks: 1 (Budgeted Time 1 Min) |

|------|------------------------------------------------------------------------------------------------------------------------|--------------------------------|

| The  | e minimum time required for the input logic levels to remain stable before the clock transition occurs is known as the |                                |

| Ansı | wer ( Please select your correct option ) VuAnswe]                                                                     | rs.com                         |

| c    | Pulse Stability time (PST)                                                                                             |                                |

| 0    | Set-up time                                                                                                            |                                |

|      | correct                                                                                                                |                                |

| c    | Hold time                                                                                                              |                                |

| c    | Pulse Interval time  Made by:                                                                                          | Waqar Siddha                   |

| Question No : 21 of 52                       | Marks: 1 (Budgeted Time 1 Min) |

|----------------------------------------------|--------------------------------|

| RCO Stands for                               |                                |

| Answer ( Please select your correct option ) | VuAnswers.com                  |

| Reconfiguration Counter Output               |                                |

| Reconfiguration Clock Output                 |                                |

| Ripple Counter Output                        |                                |

| Ripple Clock Output                          | correct Made by: Wagar Siddh   |

| Question No : 22 of 52                                                         | Marks: 1 (Budgeted Time 1 Min)                                                                                                      |

|--------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------|

| We have a digital circuit. Different parts of circuit operate<br>help by using | different clock frequencies (4MHZ, 2MHZ and 1MHZ), but we have a single clock source having a fix clock frequency (4MHZ), we can ge |

| Answer ( Please select your correct option )                                   | VuAnswers.com                                                                                                                       |

| T-Flop-Flop                                                                    | V UMITSWELS, COII                                                                                                                   |